# **Entitled:**

"On the Selection of Parts and Processes during Design of Printed Circuit Board Assemblies"

# **Authors:**

(with M.O. Ball, S. Bashyam, R.K. Karne and V.S. Trichur)

# **Conference Information:**

INRIA/IEEE Conference on Emerging Technologies and Factory Automation Paris, France October 10-13, 1995

# On the Selection of Parts and Processes during Design of Printed Circuit Board Assemblies

MICHAEL O. BALL, JOHN S. BARAS<sup>†</sup>, SRIDHAR BASHYAM, RAMESH K. KARNE<sup>†</sup> AND VINAI S. TRICHUR

Institute for Systems Research University of Maryland, College Park

March 1995

#### Abstract

We consider a multiobjective optimization model that determines components and processes for given conceptual designs of printed circuit board assemblies. Specifically, our model outputs a set of solutions that are Pareto optimal with respect to a cost and a quality metric. The discussion here broadly outlines an integer programming based solution strategy, and represents in-progress work being carried out in collaboration with a manufacturing firm.

## 1 Motivation

The advent of the concurrent engineering approach to product development has stimulated research on automated tools to support various product life cycle considerations at the design stage. In particular, for the design of printed circuit board assemblies, while software to validate the functionality of the design (for example, via simulation) has been in use for some time now; more recently, results have been reported on the development of tools that address the manufacturability of proposed scenarios. For example, Harhalakis et. al [1] have developed a decision support system for the manufacturability evaluation of Microwave Modules. Using a Group Technology approach, they carry out detailed feasibility assessment of proposed designs and also establish manufacturability ratings with respect to both electrical as well as mechanical attributes of the design. Furthermore, the system provides a feedback to the designer on changes to the current design that could potentially improve its manufacturability. The system however does not provide an explicit cost/quality assessment of the design and neither does it attempt to explore the search space of design alternatives in an automated fashion. A similar approach can be found in [2] where a knowledge-based system is described for the assembly of printed circuit boards. The literature cited in these papers indicates that rule-based expert systems has been the predominant model for manufacturability assessment of PCB assemblies. While these tools provide significant support to product designers, at the specific manufacturing facility that motivated this work, a major design concern is to systematically and explicitly evaluate potential design alternatives in terms of cost and quality. Specifically, even for a given conceptual (or functional) level design, a number of choices are available for components and processes. For example, a resistor of given specifications could be available as both leaded and surface mount types, and offered by a number of vendors with differing cost and quality ratings. These differences could, in turn, require different processes for assembly (board placement) and electrical connection (soldering). Also, in our problem setting, in which lot sizes are relatively small, we need to consider both manual as well as automated options to carry out processes such as assembly and soldering (in contrast with high

<sup>\*</sup>This work was supported in part by NSF grant No. CDR-8803012.

<sup>&</sup>lt;sup>†</sup>The work of these authors was supported in part by Westinghouse Electric Corporation and the Maryland Industrial Partnerships Program.

there are cost and quality trade-offs between the various choices. Consequently, along with the manufacturability tools reported in the literature, there is a distinct need for models that efficiently explore the search space to identify "good" design options in terms of cost and quality. In this paper, we present some initial work along these lines but limit ourselves at this stage to assessing quality only in terms of yield data. The terms quality and yield will be used interchangeably henceforth in this paper.

With respect to cost evaluation of PCB designs, schemes for costing out a given PCB design can be found in a number of sources (see, for example, [3, 4, 5]). A perusal of this body of literature however reveals the following:

- Attempts to determine optimal designs (rather than assessing a given design) based on costing mechanisms have been rather limited. Oh and Park [3] use a dynamic programming approach to optimize the assembly processes; however, their procedure does not appear to be very practical for situations having a large search space of design alternatives. The only other optimization application we have come across is Russell [6] (cf., [2]), which appears to be more along the lines of the work being reported here.

- The quality of a given design is factored into the analysis usually via a rework cost. On the other hand, we see cost and quality as competing (and often conflicting) evaluation metrics for which a *multicriteria* approach seems to be more appropriate.

We are currently developing an optimization tool with the following capabilities:

- It considers a set of alternative conceptual designs for a given application and for each design, the complete set of packaging options in terms of components and processes.

- Explicit expressions for cost and quality are developed and form the basis for exploring the search space of design options. The analysis takes into account the various subassemblies that comprise the final product.

- The problem is formulated as a multiobjective integer program and a solution procedure is proposed to efficiently output a set of Pareto optimal solutions.

While the complete details of this optimization tool along with the implementation results will be reported in a future paper, the remainder of this paper broadly outlines the modeling approach we have adopted for this project. In the next section, after defining notation and specifying the input data, we formulate our problem as a multiobjective 0-1 integer program. We then provide an outline of our solution strategy.

#### 2 Problem Definition

For ease of exposition, we will describe our approach for the following simplistic situation:

A conceptual design for the application at hand is given. The design specifies the set of required *generic* part types together with their functionality, and for each such part type, a number of specific component alternatives are considered. For each component, a process is to be selected from a given set of candidate processes. Key attributes such as material costs, runtimes, setup times and defect rates are known for parts, processes and part-process combinations. It is assumed that the entire design is to be realized via a single assembly.

The problem we consider is to determine a set of parts and processes that realizes the design in a Pareto optimal manner with respect to cost and quality.

We begin by defining some notation:

$V = \{1, 2, ..., V\} = \text{set of generic parts},$

$\mathcal{V}_{j} = \{1, 2, \dots, V_{j}\} = \text{set of alternatives for the } j \text{th generic part},$

$\mathcal{P} = \{1, 2, \dots, P\} = \text{set of processes},$

$c_j$  = unit cost of jth part:  $j \in \mathcal{V}_k$ ,  $k \in \mathcal{V}$ ,

$s_p$  = setup time of pth process:  $p \in \mathcal{P}$ ,

$t_{pj}$  = runtime when pth process is used for jth part,

$\alpha_j$  = defect rate of jth part,

$\beta_p$  = yield rate of pth process,

$n_j$  = number of parallel components to be used for jth part,

l = labor cost per unit time,

b = batch size.

Note that  $n_j$  represents a *redundancy* element that is usually considered while designing electronic devices. We assume that all the above quantities are provided as input data. We now define the following decision variables:

$$x_j = \begin{cases} 1 & \text{if part } j \text{ is selected,} \\ 0 & \text{otherwise.} \end{cases}$$

$y_p = \begin{cases} 1 & \text{if process } p \text{ is used in the assembly,} \\ 0 & \text{otherwise.} \end{cases}$

$x_{pj} = \begin{cases} 1 & \text{if process } p \text{ is selected for part } j, \\ 0 & \text{otherwise.} \end{cases}$

The expressions for cost  $(C_0)$  and quality  $(Q_0)$  are given as follows:

$$C_0 = \sum_{i} n_i c_i x_i + l \sum_{p,j} t_{pj} x_{pj} + \frac{l}{b} \sum_{p} s_p y_p, \qquad (1)$$

$$Q_0 = \prod_{p} (\beta_p)^{y_p} \prod_{j} (1 - \alpha_j^{n_j})^{x_j}.$$

(2)

The above equations are essentially derived on the following basis:

The decision variables in (1) and (2) ensure that only those elements that are selected to be in an assembly contribute to its cost and quality. We can now linearize (2) to get

$$Q_0' = \log Q_0 = \sum_{p} y_p \log \beta_p + \sum_{j} x_j \log (1 - \alpha_j^{n_j}).$$

(3)

The problem we wish to solve is the following multiobjective 0-1 integer program:

minimize

$$\left\{ \begin{array}{c} C_0 \\ -Q_0' \end{array} \right\}$$

subject to

$$\sum_{j \in \mathcal{V}_k} x_j = 1 \quad k \in \mathcal{V} \tag{4}$$

$$\sum_{\mathbf{p}\in\mathcal{P}} x_{\mathbf{p}j} = x_j \quad \forall j \tag{5}$$

$$y_p \ge x_{pj} \quad \forall p, j \tag{6}$$

$$x_j, y_p x_{pj} \in \{0, 1\} \ \forall j, p$$

(7)

It is well-known that a set of *efficient* solutions to the above problem can be obtained by solving the following *parametric* problem (P):

minimize

$$\lambda C_0 - (1 - \lambda)Q'_0$$

, (8) subject to constraints (4)-(7),

where the parameter  $\lambda$  ranges over the interval [0, 1]. It is this version of the problem that we address in our project.

## 3 Discussion

For any given  $\lambda$ , problem P directly corresponds to the well-known uncapacitated facility location problem and, consequently, is NP-Hard. However, the problem has been relatively well studied and a number of solution strategies have been reported in the operations research literature (see, for example, [7]). A tricky issue in our application here is that we would like to generate a set of Pareto optimal solutions parameterized with respect to  $\lambda$ . Hence, in selecting a solution procedure, besides efficiency and accuracy we also need to consider the ease with which parametric analysis could be carried out.

The solution approach that we propose at this time arises from the observation that the number of process alternatives involved in PCB assembly design is quite small with the key processes being

- manual or automated component placement (assembly) for surface mount and leaded parts,

- manual or wave soldering for leaded (through-hole mounted) parts, and

- manual, wave or reflow soldering for surface mount parts.

The small number of possible processes implies that an approach which starts by enumerating all possible process combinations (y vectors) is computationally feasible. We then note that for a given set of selected processes, that is, a set  $\mathcal{P}'$  such that

$$y_p = \begin{cases} 1 & \text{if } p \in \mathcal{P}', \\ 0 & \text{otherwise,} \end{cases}$$

(9)

problem P becomes easy to solve. In fact, it is easy to show that the following greedy assignment rule produces an optimal solution.

#### $GREEDY\_SOLUTION(P')$

```

for i := 1 to V /* for each generic part type */

for j := 1 to V_i /* for each alternative of the ith generic part type */

p := l \in P' : t_{lj} \le t_{mj} \ \forall m \in P' /* greedy choice of process for part j */

cost[j] := \lambda(n_j c_j + l t_{pj}) - (1 - \lambda)(1 - \alpha_j^{n_j}) /* cost out part j */

end for

choice[i] := l \in V_i : cost[l] \le cost[m] \ \forall m \in V_i /* greedily select alternative for ith generic part type */

```

#### end for

For a given set P' of selected processes, the greedy algorithm stated above first assigns the cheapest process for each part alternative. It then costs out each part alternative and subsequently selects the minimum cost alternative for each generic part type. Using strong duality, this solution can be shown to be optimal.

The greedy approach however does not permit a straightforward procedure for parametric analysis with respect to  $\lambda$ . For this purpose, consider the following reduced problem  $P(\mathcal{P}')$

minimize

$$\lambda C_0 - (1 - \lambda)Q'_0$$

, subject to constraints (4)-(7) and (9).

It can be shown that the feasible region for this problem is an integral polyhedron and hence, the linear programming (LP) relaxation to this problem is guaranteed to produce an integer solution. As such, this problem could be routinely solved using standard LP software such as LINDO or CPLEX and furthermore, full parametric analysis with respect to  $\lambda$  could also be efficiently performed.

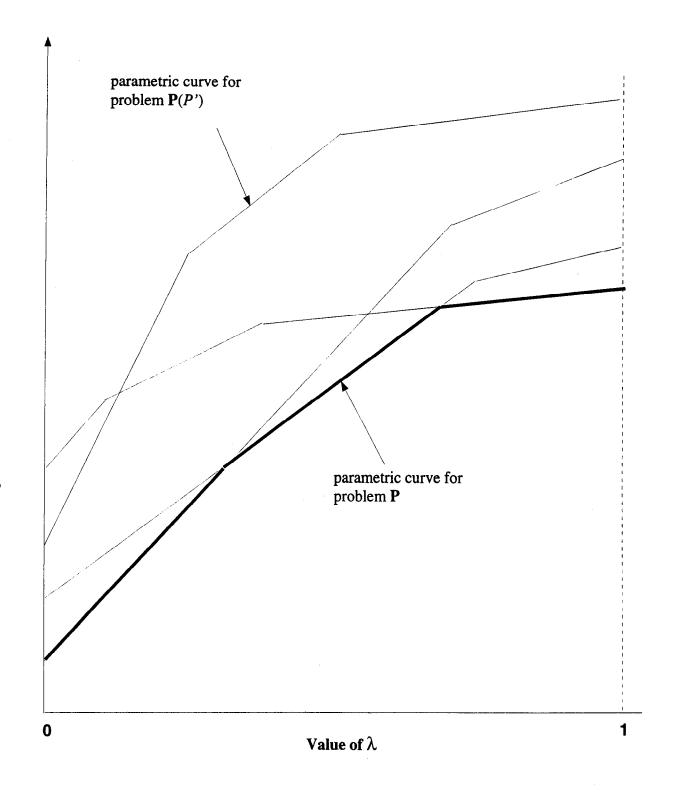

In summary, our approach is to solve  $2^{|\mathcal{P}|}$  subproblems, one for each choice for  $\mathcal{P}'$ . For each subproblem, the optimal objective function value is obtained as a piece-wise linear function of  $\lambda$ . The lower envelope of the family of these functions yields the parametric solution to the original problem **P**. The situation is shown in Figure 1.

### 4 Conclusions

In this paper, we have outlined an approach for concurrent design of PCB assemblies. In the complete application being undertaken, the analysis becomes more complex than the one presented here since we would like to model the conceptual design process in terms of a functional tree as discussed in Kusiak et. al [8] and Sturges [9]. Furthermore, we need to consider the fact that a given design is typically realized via several subassemblies that are combined in a hierarchical fashion. Other considerations such as commonality of parts and restricting the number of vendors involved would introduce additional constraints into the model. While we are in the process of applying the approach described in this paper to an extended model, other solution strategies are also being investigated. At a "systems level" perspective, the optimization model proposed provides the capability of reducing the search space to a set of design choices that are good in terms of cost and quality. This set could then be explored in greater detail by other manufacturability assessment tools such as those referenced in this paper.

## References

[1] G. Harhalakis, I. Minis, and H. Rathbun. "Manufacturability Evaluation of Electronic

- Products Using Group Technology". In Proceedings of the 1993 NSF Design and Manufacturing Systems Conference, pages 1353-1360, Charlotte, NC, 1993.

- [2] S.K. Padhy and S.N. Dwivedi. "An Object-Oriented Knowledge-Based System for Assembly of Printed Circuit Boards". In G.A. Gabriele, editor, Advances in Design Automation Volume 1, pages 43-54. ASME, 345 East 47th Street, United Engineering Center, New York, NY 10017, 1991.

- [3] C.J. Oh and C.S. Park. "An Economic Evaluation Model for Product Design Decisions under Concurrent Engineering". The Engineering Economist, 38(4):275-297, Summer 1993.

- [4] C.A.S. Heng and R.K.L. Gay. "Design For Manufacturability: Cost Analysis of Electronic Printed Circuit Board Assembly". In G.A. Gabriele, editor, Advances in Design Automation - Volume 1, pages 63-67. ASME, 345 East 47th Street, United Engineering Center, New York, NY 10017, 1991.

- [5] G. Boothroyd. Assembly Automation and Product Design. Marcel Dekker, Inc., 270 Madison Avenue, New York, NY 10016, 1992.

- [6] G.A. Russell. "Design for Assembly of Printed Circuit Boards". In Proceedings of the First International Conference on Product Design for Assembly, Newport, RI, April 15-17 1986.

- [7] G.L. Nemhauser and L.A. Wolsey. Integer and Combinatorial Optimization. John Wiley & Sons, Inc., 1988.

- [8] A. Kusiak, E. Szczerbicki, and K. Park. "A novel approach to decomposition of design specifications and search for solutions". *International Journal of Production Research*, 29(7):1391-1406, 1991.

- [9] R.H. Sturges. "A Computational Model for Conceptual Design Based on Function Logic". In Proceedings of the 1993 NSF Design and Manufacturing Systems Conference, pages 681-687, Charlotte, NC, 1993.

Figure : Parametric Analysis with respect to  $\lambda$